Efficient quantum-safe crypto chip for IoT security

Image: Utsav Banerjee

The security of modern cryptographic protocols relies on the computational hardness of various complex mathematical problems. However, they can be compromised by future large-scale quantum adversaries. This has motivated the recent emergence of post-quantum cryptography (PQC) algorithms. While being quantum-safe, these new algorithms pose challenges in terms of computation and communication overheads.

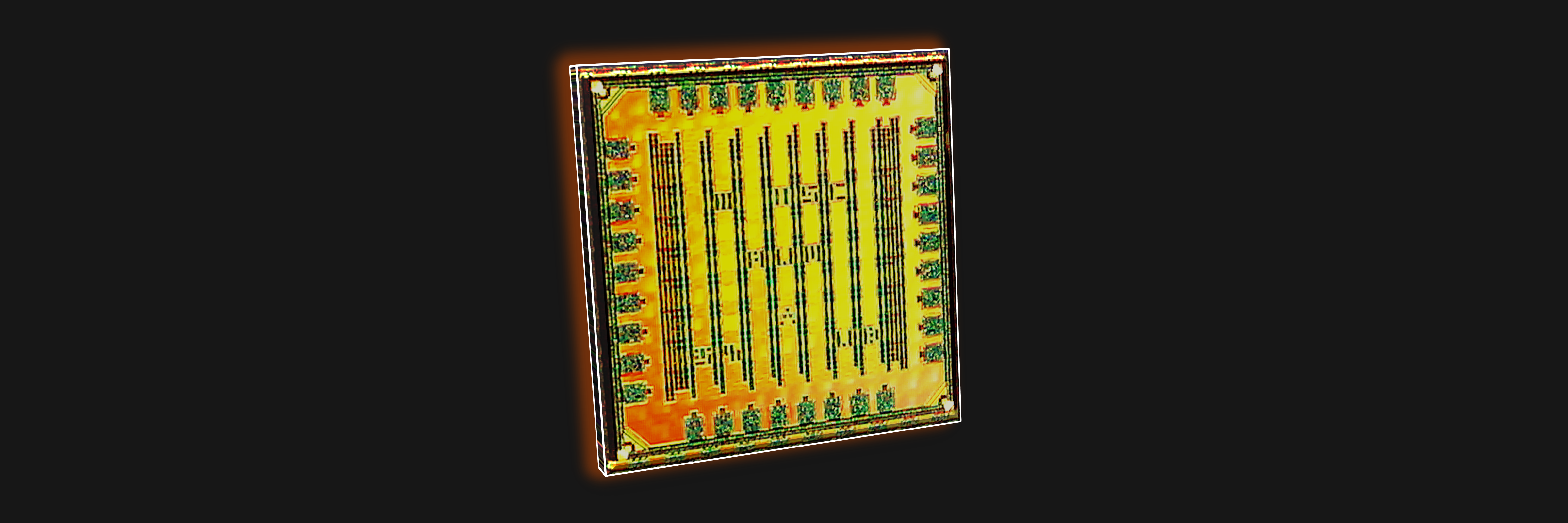

Recent work led by Utsav Banerjee, Assistant Professor in the Department of Electronic Systems Engineering (ESE), IISc and his PhD advisee Krishna Sai Tarun Ramapragada, has demonstrated a compact and low-power chip implementing quantum-safe cryptography for the Internet of Things (IoT). This is the first custom ASIC (Application-Specific Integrated Circuit) demonstration of hardware-accelerated signature verification for SQIsign, an isogeny-based digital signature scheme being considered for PQC standardisation.

SQIsign is an attractive candidate for securing IoT applications such as secure boot, firmware update, certificate validation, and server authentication, requiring verification-friendly signature algorithms with small public key and signature sizes. The IISc team has proposed several circuit innovations and algorithm-architecture co-optimisations in the underlying modular arithmetic computation, elliptic curve isogeny evaluation, and memory organisation.

Their hardware accelerator chip, implemented in 28nm CMOS technology, demonstrates SQIsign-1D uncompressed signature verification with an order of magnitude improvement in performance and energy efficiency compared to state-of-the-art assembly-optimised software.

This work was recently presented at the IEEE International Solid State Circuits Conference (ISSCC), the most premier global technical forum on advanced solid state circuits and system-on-chip designs. The results not only demonstrate SQIsign as a promising quantum-safe digital signature candidate for IoT applications but also pave the way for future research on hardware-accelerated isogeny-based post-quantum cryptography.

REFERENCE:

Ramapragada KST, Banerjee U, A 0.05mm2 1.19-to-7.34mW SQIsign-1d isogeny-based post-quantum signature verification accelerator for IoT, IEEE International Solid-State Circuits Conference (ISSCC) (2026).

https://ieeexplore.ieee.org/document/11408981

LAB WEBSITE:

https://labs.dese.iisc.ac.in/sinesyslab